Babak Falsafi T. N. Vijaykumar (Eds.)

# LNCS 3164

# Power - Aware Computer Systems

Third International Workshop, PACS 2003 San Diego, CA, USA, December 2003 Revised Papers

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich. Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos New York University, NY, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Babak Falsafi T.N. Vijaykumar (Eds.)

# Power - Aware Computer Systems

Third International Workshop, PACS 2003 San Diego, CA, USA, December 1, 2003 Revised Papers

Volume Editors

Babak Falsafi Carnegie Mellon University Electrical and Computer Engineering, Computer Science 5000 Forbes Avenue, Pittsburgh, PA 15213, USA E-mail: babak@cmu.edu

T.N. Vijaykumar Purdue University School of Electrical and Computer Engineering, Department of Computer Science 465 Northwestern Avenue, West Lafayette, Indiana 47907-1285, USA E-mail: vijay@ecn.purdue.edu

Library of Congress Control Number: Applied for

CR Subject Classification (1998): B.7, B.8, C.1, C.2, C.3, C.4, D.4

ISSN 0302-9743 ISBN 3-540-24031-4 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springeronline.com

© Springer-Verlag Berlin Heidelberg 2004 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11364641 06/3142 5 4 3 2 1 0

# Preface

Welcome to the proceedings of the 3rd Power-Aware Computer Systems (PACS 2003) Workshop held in conjunction with the 36th Annual International Symposium on Microarchitecture (MICRO-36). The increase in power and energy dissipation in computer systems has begun to limit performance and has also resulted in higher cost and lower reliability. The increase also implies reduced battery life in portable systems. Because of the magnitude of the problem, all levels of computer systems, including circuits, architectures, and software, are being employed to address power and energy issues. PACS 2003 was the third workshop in its series to explore power- and energy-awareness at all levels of computer systems and brought together experts from academia and industry.

These proceedings include 14 research papers, selected from 43 submissions, spanning a wide spectrum of areas in power-aware systems. We have grouped the papers into the following categories: (1) compilers, (2) embedded systems, (3) microarchitectures, and (4) cache and memory systems.

The first paper on compiler techniques proposes pointer reuse analysis that is biased by runtime information (i.e., the targets of pointers are determined based on the likelihood of their occurrence at runtime) to map accesses to energyefficient memory access paths (e.g., avoid tag match). Another paper proposes compiling multiple programs together so that disk accesses across the programs can be synchronized to achieve longer sleep times in disks than if the programs are optimized separately.

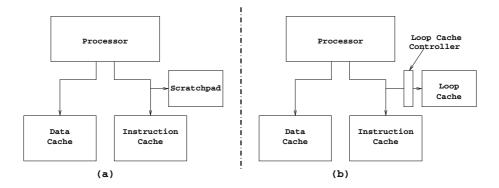

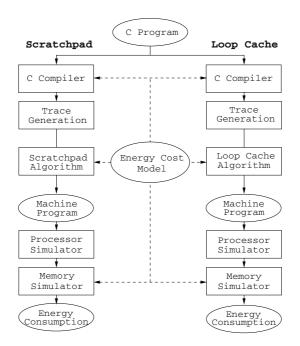

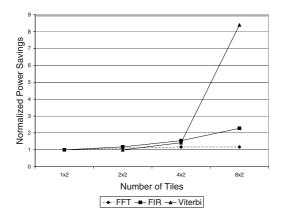

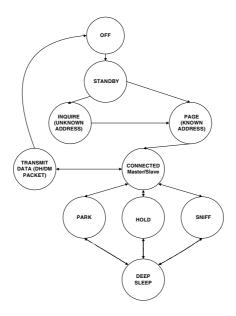

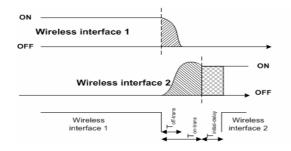

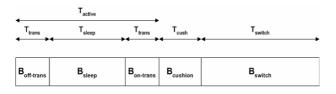

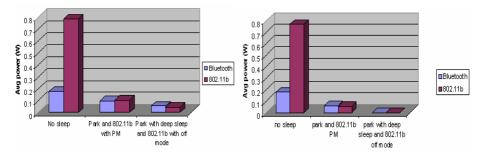

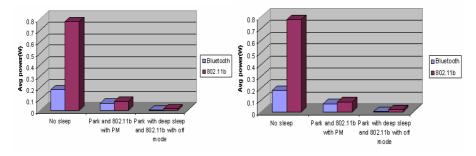

The first paper on embedded systems proposes scaling down the components (display, wireless, and CPU) of a mobile system to match user requirements while reducing energy. The second paper explores an integer linear programming approach for embedded systems to decide which instructions should be held in a low-power scratchpad instead of a high-power instruction cache. The next paper predicts battery life at runtime to help the operating system in managing power. The next paper proposes a tiled architecture that exploits parallelism enabled by global interconnects and synchronized design to achieve high energy efficiency. The last paper in this group proposes a policy to decide which of the multiple wireless network interfaces provided in a mobile device should be used based on the power and performance needs of the mobile system.

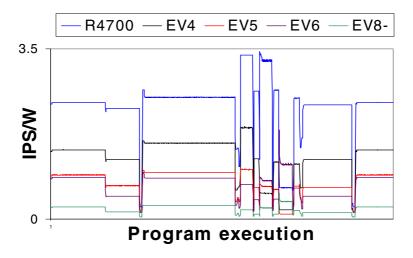

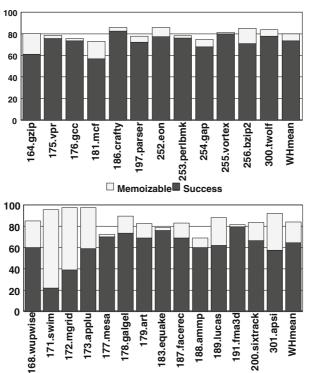

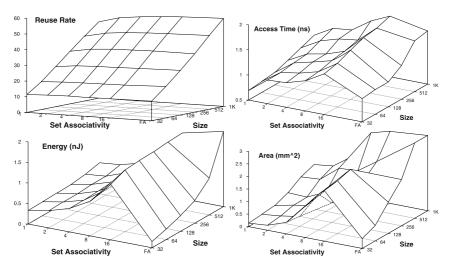

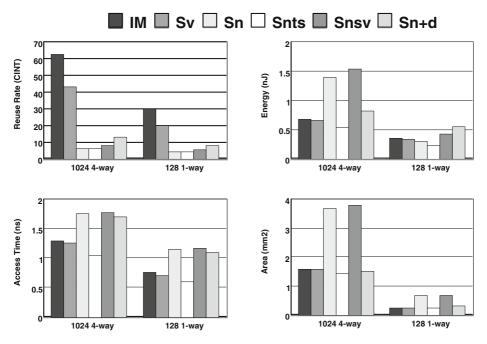

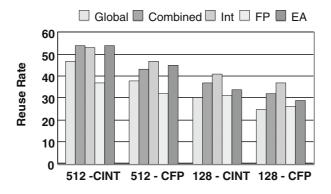

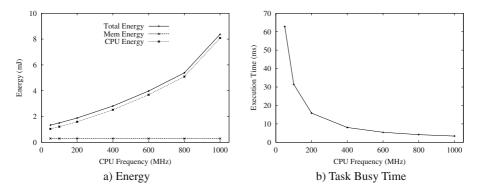

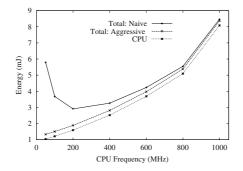

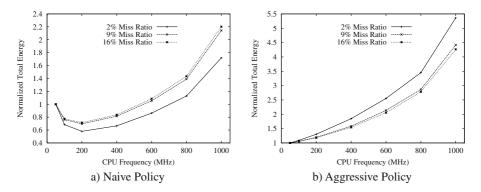

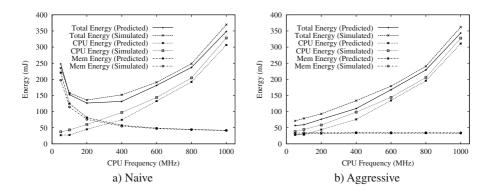

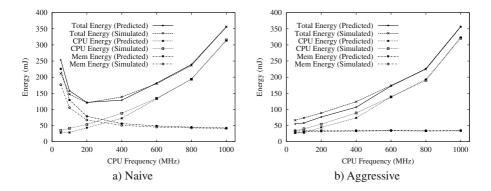

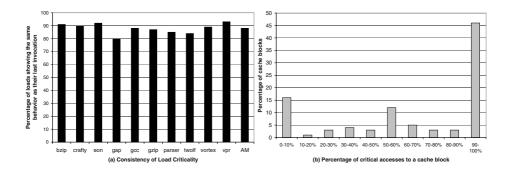

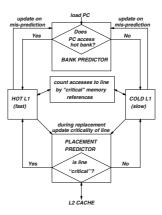

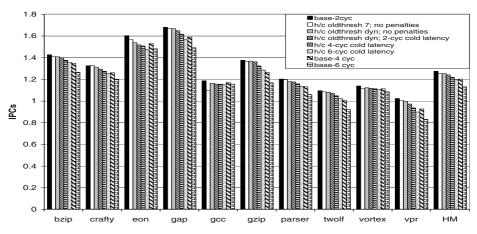

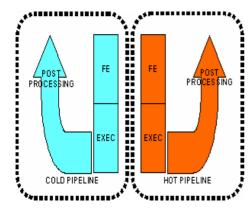

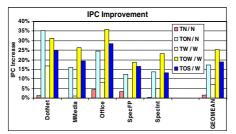

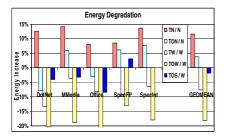

The third group of papers focuses on microarchitecture techniques, and includes an analysis of energy, area, and speed trade-offs between table lookup for instruction reuse and actual computation. Another paper proposes scheduling transactions in a multiprocessor to as few CPUs as possible to increase the number of CPUs in deep-sleep state. The next paper evaluates the extent of energy savings achieved by avoiding instructions that are either not needed for correct behavior or not committed, and by sizing microarchitectural structures. The last paper proposes coupled power and thermal simulation and studies the effect of temperature on leakage energy. The last group proposes techniques to reduce power in caches and memory. The first paper in this group studies the interaction between dynamic voltage scaling (DVS) and power-aware memories and proposes policies to control the CPU's DVS setting and the memory's power setting together. The next paper uses the criticality of instructions to determine which locations should be placed in high-speed cache banks and which in low-power banks. The last paper proposes applying high-performance techniques only to the most-frequently-used instruction traces and saving power on the other traces.

PACS 2003 was successful due to the quality of the submissions, the efforts of the program committee, and the attendees. We would like to thank Pradip Bose for his interesting keynote address, which described microarchitectural choices at the early architecture-definition stage to achieve power and energy efficiency. We would like to also thank Glen Reinman, Jason Fritts, and the other members of the MICRO-36 organizing committee who helped arrange the local accommodations and publicize the workshop.

December 2003

Babak Falsafi and T.N. Vijaykumar

## PACS 2003 Program Committee

Babak Falsafi, Carnegie Mellon University (co-chair) T.N. Vijaykumar, Purdue University (co-chair)

Sarita Adve, University of Illinois David Albonesi, University of Rochester David Blaauw, University of Michigan Pradip Bose, IBM David Brooks, Harvard University George Cai, Intel Keith Farkas, Hewlett-Packard Yung-Hsiang Lu, Purdue University Mahmut Kandemir, Pennsylvania State University Ulrich Kremer, Rutgers University Diana Marculescu, Carnegie Mellon University Andreas Moshovos, University of Toronto Farid Najm, University of Toronto Daniel Mosse, University of Pittsburgh Raj Rajkumar, Carnegie Mellon University Hazim Shafi, IBM Josep Torrelas, University of Illinois Amin Vahdat, Duke University

# Table of Contents

## Compilers

| Runtime Biased Pointer Reuse Analysis and Its Application to Energy             |    |

|---------------------------------------------------------------------------------|----|

| Efficiency                                                                      |    |

| Yao Guo, Saurabh Chheda, Csaba Andras Moritz                                    | 1  |

| Inter-program Compilation for Disk Energy Reduction<br>Jerry Hom, Ulrich Kremer | 13 |

## Embedded Systems

| Energy Consumption in Mobile Devices: Why Future Systems Need         |    |

|-----------------------------------------------------------------------|----|

| Requirements-Aware Energy Scale-Down                                  |    |

| Robert N. Mayo, Parthasarathy Ranganathan                             | 26 |

| Efficient Scratchpad Allocation Algorithms for Energy Constrained     |    |

| Embedded Systems                                                      |    |

| Manish Verma, Lars Wehmeyer, Peter Marwedel                           | 41 |

| Online Prediction of Battery Lifetime for Embedded and Mobile Devices |    |

| Ye Wen, Rich Wolski, Chandra Krintz                                   | 57 |

| Synchroscalar: Initial Lessons in Power-Aware Design of a Tile-Based  |    |

| Embedded Architecture                                                 |    |

| John Oliver, Ravishankar Rao, Paul Sultana, Jedidiah Crandall,        |    |

| Erik Czernikowski, Leslie W. Jones IV, Dean Copsey, Diana Keen,       |    |

| Venkatesh Akella, Frederic T. Chong                                   | 73 |

| Heterogeneous Wireless Network Management                             |    |

| Wajahat Qadeer, Tajana Simunic Rosing, John Ankcorn,                  |    |

| Venky Krishnan, Givanni De Micheli                                    | 86 |

|                                                                       |    |

#### Microarchitectural Techniques

| "Look It Up" or "Do the Math": An Energy, Area, and Timing |     |

|------------------------------------------------------------|-----|

| Analysis of Instruction Reuse and Memoization              |     |

| Daniel Citron, Dror G. Feitelson                           | 101 |

|                                                            |     |

| CPU Packing for Multiprocessor Power Reduction             |     |

| Soraya Ghiasi, Wes Felter                                  | 117 |

| Exploring the Potential of Architecture-Level Power Optimizations |     |

|-------------------------------------------------------------------|-----|

| John S. Seng, Dean M. Tullsen                                     | 132 |

|                                                                   |     |

| Coupled Power and Thermal Simulation with Active Cooling          |     |

| Weiping Liao, Lei He                                              | 148 |

# Cache and Memory Systems

| The Synergy Between Power-Aware Memory Systems and Processor                                                                                                    |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Voltage Scaling                                                                                                                                                 |     |

| Xiaobo Fan, Carla S. Ellis, Alvin R. Lebeck                                                                                                                     | 164 |

| Hot-and-Cold: Using Criticality in the Design of Energy-Efficient Caches<br>Rajeev Balasubramonian, Viji Srinivasan, Sandhya Dwarkadas,<br>Alper Buyuktosunoglu | 180 |

| PARROT: Power Awareness Through Selective Dynamically Optimized<br>Traces                                                                                       |     |

| Roni Rosner, Yoav Almog, Micha Moffie, Naftali Schwartz,<br>Avi Mendelson                                                                                       | 196 |

| Author Index                                                                                                                                                    | 215 |

# Runtime Biased Pointer Reuse Analysis and Its Application to Energy Efficiency

Yao Guo, Saurabh Chheda, and Csaba Andras Moritz

Department of Electrical and Computer Engineering, University of Massachusetts, Amherst, MA 01003 {yaoguo, schheda, andras}@ecs.umass.edu

Abstract. Compiler-enabled memory systems have been successful in reducing chip energy consumption. A major challenge lies in their applicability in the context of complex pointer-intensive programs. State-ofthe-art high precision pointer analysis techniques have limitations when applied to such programs, and therefore have restricted use. This paper describes runtime biased pointer reuse analysis to capture the behavior of pointers in programs of arbitrary complexity. The proposed technique is runtime biased and speculative in the sense that the possible targets for each pointer access are statically predicted based on the likelihood of their occurrence at runtime, rather than conservative static analysis alone. This idea implemented as a flow-sensitive dataflow analysis enables high precision in capturing pointer behavior, reduces complexity, and extends the approach to arbitrary programs. Besides memory accesses with good reuse/locality, the technique identifies irregular accesses that typically result in energy and performance penalties when managed statically. The approach is validated in the context of a compiler managed memory system targeting energy efficiency. On a suite of pointer-intensive benchmarks, the techniques increase the fraction of memory accesses that can be mapped statically to energy efficient memory access paths by 7-72%, giving a 4-31% additional L1 data cache energy reduction.

#### 1 Introduction

The memory system, including caches, consumes a significant fraction of the total system power. For example, the caches and translation look-aside buffers (TLB) combined consume 23% of the total power in the Alpha 21264 [7], and the caches alone use 42% of the power in the StrongARM 110 [8]. Recent studies have proposed compiler-enabled cache designs [2, 12, 14] to improve cache performance as well as energy consumption. A major challenge, however, is their applicability when dealing with complex pointer-intensive programs. This paper presents a new approach to deal with complex pointer-intensive programs in such schemes based on the idea of runtime biased pointer reuse analysis. In addition to compiler-enabled memory systems, applications such as compiler-based prefetching, software-based memory dependence speculation, and parallelization, could also significantly benefit from the techniques presented in this paper.

Many researchers have focused on program locality/reuse analysis for arraybased memory accesses [9, 15, 16]. In general, array accesses are more regular than pointer-based memory accesses because arrays are normally accessed sequentially while pointers typically have more complicated behavior. Array based accesses are also relatively easy to deal with as type information is available to guide the analysis.

Intensive use of pointers makes however program analysis difficult since a pointer may point to different locations during execution time; the set of all locations a pointer can access at runtime is typically referred to as the *location set*. This difficulty is further accentuated in the context of large and/or complex programs. For example, more precise dataflow-based implementations of pointer analysis have limitations (e.g., often cannot complete analysis) when used for large programs or when special constructs such as pointer based calls, recursion, or library calls are found in the program. The less precise alias analysis techniques (e.g., those that are flow-insensitive) have lower complexities but don't provide precise enough static information about pointer location sets.

Our objective is to develop new techniques to capture pointer behavior that can be used to analyze complex applications with no restrictions, while providing good precision. The idea is to determine pointer behavior by capturing the frequent locations for each pointer rather than all the locations as conservative analysis would do. Predicted pointer reuse is therefore runtime biased and speculative in the sense that the possible targets for each pointer access are statically predicted/speculated based on the likelihood of their occurrence at run-time. The approach enables lower complexity and possibly higher precision analysis than traditional dataflow based approaches because locations predicted to be infrequently accessed are not considered as possible targets. The approach is applicable in all architecture optimizations that use some kind of compiler-exposed speculation hardware and when absolute correctness of static information leveraged is not necessary. This includes for example compiler managed energy-aware memory systems, compiler managed prefetching, and speculative parallelization and synchronization - these applications by their design would benefit from precise memory behavior information and would tolerate occasional incorrect static control information.

This paper shows the application of the proposed pointer techniques to an energy-efficient compiler-enabled memory management system published previously, called Cool-Mem [2]. The Cool-Mem architecture achieves energy reduction by implementing energy efficient statically managed access paths in addition to the conventional ones. The compiler decides which path is used based on static information extracted. For accesses that reuse the same cache line, cache mapping information is maintained to help eliminate redundancy in cache disambiguation. Whenever the compiler can correctly channel data memory accesses to the static access path, significant energy reduction is achieved; the statically managed access path does not need Tag access and associative lookup in RAM-Tag caches, and Tag access in CAM-Tag caches. We show that the Cool-Mem architecture, if extended with our techniques, is able to handle pointer based accesses and achieve up to 30% additional energy savings in the L1 data cache.

The rest of this paper is structured as follows. Section 2 presents the runtime biased compiler analysis techniques, including pointer analysis, distance analysis, and reuse analysis algorithms. Following this, Sect. 3 provides an overview of the compiler-enabled memory framework used for simulation and Sect. 4 shows the experimental framework. Finally, Sect. 5 gives the experimental results gathered through simulation, and we conclude with Sect. 6.

#### 2 Compiler Analysis

The runtime biased (RB) pointer reuse analysis can be separated into a series of three steps: RB pointer analysis, RB distance analysis, and RB reuse analysis.

*RB Pointer Analysis* is first applied in order to gather basic pointer information needed to predict pointer access patterns. A flow-sensitive dataflow scheme is used in our implementation. Flow-sensitive analysis maintains high precision (i.e., the location set of each pointer access is determined in a flow-sensitive manner even if based on the same variable). Our analysis is guided by reevaluating, at each pointer dereference point, the (likely) runtime frequency of each location a pointer can point to. For example, possible locations that are from definitions in outer loop-nests are marked or not included when the pointer is dereferenced in inner loops and if at least one new location has been defined in the inner loop. Conventional analysis would not distinguish between these locations.

Precise conventional pointer analysis usually requires that the program includes all its source codes, for all the procedures, including static libraries. Otherwise, the analysis cannot be performed. Precise conventional pointer analysis is often used in program optimizations where conservative assumption must be made - any speculation could result in incorrect execution.

In contrast, our approach does not require the same type of strict correctness. If the behavior of a specific pointer cannot be inferred precisely, we can often speculate or just ignore its effect. For example, if a points-to relation (or location) cannot be inferred statically, we speculatively consider only the other locations gathered in the pointer's location set. We mark the location as undefined. When assigning location sets for the same pointer at a later point in the CFG, one could safely ignore/remove the *undefined location* in the set, if the probability of the pointer accessing that location, at the new program point, is low (e.g., less than 25% in our case).

The main steps of our RB pointer analysis algorithm are as follows: (1) build a control-flow graph (CFG) of the computation, (2) analyze each basic block in the CFG gradually building a PTG, (3) at the beginning of each basic block merge location set information from previous basic blocks, (4) mark locations in the location sets that are unlikely to occur at runtime, at the current program point, as less frequent, (5) mark undefined locations or point-to relations; (6) repeat steps 2-5 until the PTG graph does not change (i.e., full convergence is reached) or until the allowed number of iterations are reached.

Library calls that may modify pointer values and for which source codes are not available are currently speculatively ignored. If a pointer is passed in as an argument, its location set after the call-point in the caller procedure will be marked as speculative, signaling that the location set of the pointer might be incomplete after the call. In none of the programs we have analyzed we have found library modified pointer behavior to be a considerable factor in gathering precise pointer reuse information.

*RB Distance Analysis* gathers stride information for pointers changing across loop iterations. This stride information is used to predict pointer-based memory access patterns, and speculation is performed whenever the stride is not fixed. As strides could change in function of the paths taken in the Control-Flow Graph (CFG) of the loop body, only the most likely strides (based on static branch prediction) are considered.

In the example shown in Fig. 1(a), the value of pointer p changes after each iteration. In general, there are two ways to deal with this situation if implemented as part of pointer analysis. Each element in the array structure could be treated as a different location, or, another approach would be to treat the whole array *arr* as a single location. The former is too complicated for compiler analysis while the latter is not precise enough.

In our approach, as shown in Fig. 1(a), we first find the initial location for p. Then, when we find out that p is changing for each iteration, we calculate the distance (stride) between the current location and the location after modification. If the distance is constant, we will use both the initial location and distance to describe the behavior of the pointer.

Extracting stride information is not always easy. In Fig. 1(a), we can easily calculate that the stride for pointer p is 4 bytes. However, for the example in Fig. 1(b), the stride for pointer p is variable since we do not know what value procedure foo() will return. In this case, we can use speculation based on static

Fig. 1. Distance analysis examples: (a) static stride (b) variable stride

information related to the location set to estimate the stride. For example, the information we do know is (1) p points to array arr and (2) the size of array arr is small. Based on this information, we can speculate that the stride of p is small although we do not know the exact number.

Another example of stride prediction, as also mentioned earlier, is ignoring strides that are less likely to occur at runtime based on static branch prediction. Clearly, depending on which path is executed at runtime the stride of a pointer might change across loop iterations, as not all the possible paths leading to that pointer access are equally likely to occur.

*RB Reuse Analysis* attempts to discover those pointer accesses that have reuse, i.e., refer to the same cache line. Reuse analysis uses the information provided by the previous analyses to decide whether two pointer accesses refer to the same cache line. Based on the reuse patterns, pointer accesses are partitioned into reuse equivalence classes. Pointers in each equivalence class have a high probability of referring to the same cache line during execution and will be mapped through the static access path in the Cool-Mem system.

Reuse analysis for array-based accesses has been studied and used in [9, 15, 16]. For pointer-intensive programs, we use a classification scheme similar to theirs, but we redefine it specifically in the context of pointer-based accesses.

- 1. *Temporal Reuse*: This is the case when a pointer is not changing during loop iterations. This is the simplest case for loop-based accesses.

- 2. *Self-Spatial Reuse*: If a pointer is changing using a constant stride and the stride is small enough, two or more consecutive accesses will refer to the same cache line.

- 3. *Group-Spatial Reuse*: A group of pointers can share the same cache line during each loop iteration even when they do not exhibit self-spatial reuse.

- 4. Simple-Spatial Reuse: This exists between two pointers that refer to the same cache line but do not belong to any loop. Simple-spatial reuse is added as a new reuse category because we find that this situation is important for pointer-based programs although it is not as important for array-based programs. The reason for this is that array structures are typically accessed using loops, while pointer-based data structures are often accessed using recursive functions.

Pointer-based memory accesses are partitioned into different *reuse equivalence classes* based on the reuse classification and strides. A reuse equivalence relation exists between two memory accesses if one of the above mentioned reuse relations exists between them. Intuitively, each reuse equivalence class contains those pointer accesses that have a good chance to access the same cache line.

Once we have the reuse equivalence classes, we use a *reuse probability threshold* to decide which of the equivalence classes will likely have high cache line reuse. All the accesses assigned to an equivalence class with a reuse probability smaller than this threshold or not assigned to a class, will be regarded as irregular. In our experiments, we choose the reuse threshold such that the statically estimated reuse misprediction rate is predicted to be smaller than 33%

(the overall misprediction rate could be much lower depending on the mixture of equivalence classes, but could also be larger due to the speculative nature of the information this analysis is based on).

After RB reuse analysis, all the accesses which fall into one of the four reuse categories are regarded as having good reuse possibility. Pointer accesses which have bad locality and small reuse chances are identified as irregular accesses.

#### 3 Application: Compiler-Managed Memory Systems

The results of run-time biased reuse analysis can be applied to general-purpose compiler-enabled cache management systems. In this paper, we replicated a compiler-enabled energy efficient cache management framework, Cool-Mem [2], and extended it by incorporating our pointer reuse analysis techniques. We will give a simple introduction of Cool-Mem architecture in this section, detail information about Cool-Mem can be found in [2].

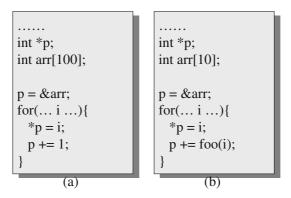

#### 3.1 Cool-Mem Memory System

Figure 2 presents an overview of the Cool-Mem memory system, with integrated static and dynamic access paths. Cool-Mem extends the conventional associative cache lookup mechanism with simpler, direct addressing modes, in a virtually tagged and indexed cache organization. This direct addressing mechanism eliminates the associative tag-checks and data-array accesses. The compiler-managed speculative direct addressing mechanisms uses the hotline registers. Static mispredictions are directed to the CAM based Tag-Cache, a structure storing cache line addresses for the most recently accessed cache lines. Tag-Cache hits also directly address the cache, and the conventional associative lookup mechanism is used only on Tag-Cache misses.

The conventional associative lookup approach requires 4 parallel tag-checks and data-array accesses(in a 4-way cache). Depending on the matching tag, one of the 4 cache lines is selected and the rest discarded. Now for sequences of accesses mapping to the same cache line, the conventional mechanism is highly redundant: the same cache line and tag match on each access. Cool-Mem reduces this redundancy by identifying at compile-time, access likely to lie in the same cache line, and mapping them speculatively through one of the hotline registers (step 1 in Fig. 2).

Different hotline compiler techniques are used to predict which cache accesses are put into which hotline registers. A simple run-time comparison (step 2) reveals if the static prediction is correct. The cache is directly accessed on correct prediction (step 3), and the hotline register updated with the new information on mis-predictions.

Another energy-efficient cache access path in Cool-Mem is the CAM-based Tag-Cache. It is used both for static mis-prediction (hotline misses) and accesses not mapped through the hotline registers, i.e. dynamic accesses (step 4). Hence it serves the dual-role of complementing the compiler-mapped static accesses

Fig. 2. Cool-Mem Architecture

by storing cache-line addresses recently replaced from the hotline registers, and also saving cache energy for dynamic accesses; the cache is directly accessed on Tag-Cache hits(step 3).

Although the Tag-Cache access is very quick, we assume that the Tag-Cache, accessed on hotline misses, require another cycle, with an overall latency similar to a regular cache access. A miss in the Tag-Cache implies that we fall back to the conventional associative lookup mechanism with and additional cycle performance overhead (step 5). The Tag-Cache is also updated with new information on misses. As seen in Fig. 2, each Tag-Cache entry is exactly the same as a hotline register, and performs the same functions, but dynamically.

#### 3.2 Cool-Mem Compiler

Cool-Mem compiler is responsible for identifying groups of accesses likely to map to the same cache-line, and mapping them through one of the hotline registers. Hotline passes are implemented in two different compiler techniques: (1) Optimistic Hotlines, where the compiler tries to map all accesses through the hotline registers, and (2) Conservative Hotlines, which maps a subset of the accesses that are more regular in nature and as a result, are likely to cause fewer mis-predictions. The description of both algorithms can be found in [2]. Both the optimistic and conservative hotline approaches are not dealing with pointer variables, because pointer information is unknown without pointer alias analysis or points-to analysis. Runtime biased pointer reuse analysis results can be applied easily in the context of the Cool-Mem architecture. Simply, pointer accesses in reuse equivalence classes with reuse attributes larger than the reuse threshold are mapped to static energy-saving cache access paths. At the same time, irregular pointers identified during reuse analysis will be directed to regular cache access paths to avoid energy and performance penalties.

#### 4 Experimental Framework

The SUIF [13]/Machsuif [11] suite is used as our compiler infrastructure. RB pointer and distance analysis is implemented as a SUIF pass which analyzes an intermediate SUIF file and then writes the pointer and stride information back as annotations. RB reuse analysis runs after the pointer analysis pass and writes reuse equivalence class information to the SUIF intermediate file.

The source files are first compiled into SUIF code and merged into one file. All high-level compiler analysis passes, including the pointer and reuse analysis passes, operate at this stage. The annotations from SUIF files are propagated to an *Alpha* binary file through the intermediate stages. We use the SimpleScalar [5] simulator with Wattch [4] extensions for collecting performance and energy numbers. This simulator, capable of running statically linked alpha binaries, has been modified to accommodate the Cool-Mem architecture.

We assume a 4-way in-order Alpha ISA compatible processor and 64 Kbyte 4way set-associative L1 caches, 0.18 micron technology, and 2.0V  $V_{dd}$ . We account for all the introduced overheads and static mispredictions in the architecture as described in [2].

We simulated a number of benchmarks during the selection process, including SPEC 2000 [1], Olden pointer-intensive benchmark suite [10] and several benchmarks used previously by the pointer analysis community [3, 6]. We chose seven benchmarks (shown in Table 1) which contain at least 25% of pointer accesses at runtime.

| Benchmark | Source   | Description                |

|-----------|----------|----------------------------|

| backprop  | Austin   | Neural network training    |

| em3d      | Olden    | Elect. magn. wave propag.  |

| ft        | Austin   | Minimum spanning tree      |

| ks        | Austin   | Graph Partition            |

| 08.main   |          | Polygon rotation           |

| mcf       | SPEC2000 | Combinatorial optimization |

| 09.vor    | McGill   | Voronoi diagrams           |

Table 1. Benchmarks used in simulation results

#### 5 Results

In this section, we show experimental results for the above benchmarks, including benchmark statistics as well as energy saving results collected using Wattch.

#### 5.1 Regular Versus Irregular Pointers

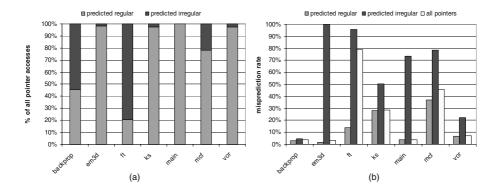

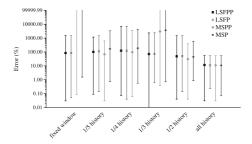

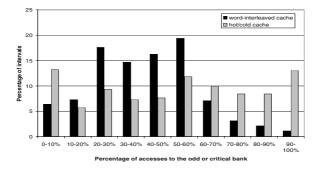

Identifying those pointers which do not have good locality is important because they normally result in energy and performance penalties when managed statically. Figure 3(a) shows the percentage of irregular pointers found during static compiler analysis. Different programs have a different portion of irregular pointers. In some of them, such as *main* and *em3d*, up to 99% of all the pointers are predicted as regular. Other programs like ft have almost 80% irregular accesses.

Figure 3(b) shows the misprediction rate of the pointers predicted when mapped to the static cache access path. The misprediction rate refers to the accesses that do not point to the cache line predicted. As shown in the second bar, the misprediction rate for irregular pointers, if mapped through the energy efficient cache access path, is very high for most of the programs. It is at least twice the misprediction rate of those pointers we identified as regular pointers. The only exception is *backprop*, which operates on a relatively small data structure, such that all the pointer accesses have very good locality. However, we can see that the misprediction rate for irregular pointers in *backprop* is still much higher than those of regular pointers.

We also show the misprediction rate for the case when all the pointer accesses are mapped through the static path. Note that the misprediction rate is significantly reduced by removing the irregular pointer accesses. For em3d, the overall misprediction rate is reduced by almost 50% while identifying only 1.7% of all

Fig. 3. Regular versus irregular pointers: (a) runtime percentage of statically determined regular and irregular pointers; (b) Static misprediction rates of pointer accesses when mapped to Cool-Mem's static cache access path. Misprediction occurs when a pointer that is predicted to have high reuse statically will not access the predicted cache line at runtime

Fig. 4. Normalized L1 D-cache energy consumption

the pointer accesses as irregular. We also identified almost 80% of all pointers as irregular in ft, which have a misprediction rate greater than 95%.

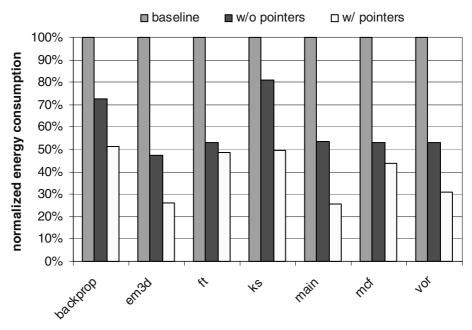

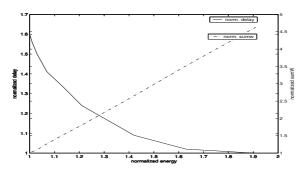

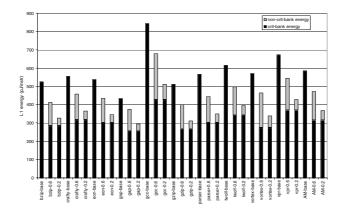

#### 5.2 Energy Savings

Figure 4 shows the energy consumption results which are normalized to the unoptimized hardware baseline architecture. The baseline energy number, which is shown as 100%, is the first bar. The second bar shows the normalized energy consumption by applying the published Cool-Mem techniques without mapping the pointer-based accesses through the statically managed cache access path. Finally, the energy consumption number, which uses the results of our reuse analysis for pointer-based accesses, is shown last. Compared to the optimization which maps only array-based accesses, 4% to 31% extra energy reduction is achieved on the L1 data cache energy consumption by mapping the pointer-based memory accesses that are statically predicted as regular through the statically managed cache access path.

#### 6 Conclusion

Compiler-enabled cache management for pointer-intensive programs is challenging because pointer analysis is difficult and sometimes even impossible for large or complex programs. By applying the runtime biased pointer analysis techniques, we can always complete analysis for any pointer-intensive program without any constraints. The techniques proposed increase the fraction of memory accesses that can be mapped statically to energy efficient cache access paths and shows significant additional energy reduction in the L1 data cache.

Our future work includes further investigation and experiments on the runtime biased pointer analysis approach and applying the analysis to other compilerenabled techniques such as compiler-directed prefetching on pointer-intensive codes.

#### References

- 1. The standard performance evaluation corporation, 2000. http://www.spec.org.

- R. Ashok, S. Chheda, and C. A. Moritz. Cool-mem: Combining statically speculative memory accessing with selective address translation for energy efficiency. In ASPLOS, 2002.

- T. Austin. Pointer-intensive benchmark suite, version 1.1, 1995. http:// www.cs.wisc.edu/~austin/ptr-dist.html.

- D. Brooks, V. Tiwari, and M. Martonosi. Wattch: A framework for architecturallevel power analysis and optimizations. In *Proceedings of the 27th Annual International Symposium on Computer Architecture*, pages 83–94, Vancouver, British Columbia, June 12–14, 2000. IEEE Computer Society and ACM SIGARCH.

- D. C. Burger and T. M. Austin. The simplescalar tool set, version 2.0. Technical Report CS-TR-1997-1342, University of Wisconsin, Madison, June 1997.

- M. Emami, R. Ghiya, and L. J. Hendren. Context-sensitive interprocedural pointsto analysis in the presence of function pointers. In SIGPLAN Conference on Programming Language Design and Implementation, pages 242–256, 1994.

- M. K. Gowan, L. L. Biro, and D. B. Jackson. Power considerations in the design of the alpha 21264 microprocessor. In *Proceedings of the 1998 Conference on Design Automation (DAC-98)*, pages 726–731, Los Alamitos, CA, June 15–19 1998. ACM/IEEE.

- J. Montanaro, R. T. Witek, K. Anne, A. J. Black, E. M. Cooper, D. W. Dobberpuhl, P. M. Donahue, J. Eno, G. W. Hoeppner, D. Kruckemyer, T. H. Lee, P. C. M. Lin, L. Madden, D. Murray, M. H. Pearce, S. Santhanam, K. J. Snyder, R. Stephany, and S. C. Thierauf. A 160-MHz, 32-b, 0.5-W CMOS RISC microprocessor. *Digital Technical Journal of Digital Equipment Corporation*, 9(1), 1997.

- 9. T. Mowry. *Tolerating Latency Through Software Controlled Data Prefetching*. PhD thesis, Dept. of Computer Science, Stanford University, Mar. 1994.

- A. Rogers, M. C. Carlisle, J. H. Reppy, and L. J. Hendren. Supporting dynamic data structures on distributed-memory machines. ACM Transactions on Programming Languages and Systems, 17(2):233–263, Mar. 1995.

- 11. M. Smith. Extending suif for machine-dependent optimizations. In *Proc. First* SUIF Compiler Workshop, Jan. 1996.

- O. S. Unsal, R. Ashok, I. Koren, C. M. Krishna, and C. A. Moritz. Cool-cache for hot multimedia. In *Proceedings of the 34th annual ACM/IEEE international* symposium on *Microarchitecture*, pages 274–283. IEEE Computer Society, 2001.

- R. Wilson, R. French, C. Wilson, S. Amarasinghe, J. Anderson, S. Tjiang, S.-W. Liao, C.-W. Tseng, M. W. Hall, M. Lam, and J. L. Hennessy. SUIF: A parallelizing and optimizing research compiler. Technical Report CSL-TR-94-620, Computer Systems Laboratory, Stanford University, May 1994.

- 14. E. Witchel, S. Larsen, C. S. Ananian, and K. Asanović. Direct addressed caches for reduced power consumption. In *Proceedings of the 34th Annual International Symposium on Microarchitecture*, pages 124–133, Austin, Texas, Dec. 1–5, 2001. IEEE Computer Society TC-MICRO and ACM SIGMICRO.

- M. E. Wolf. Improving Locality and Parallelism in Nested Loops. PhD thesis, Dept. of Computer Science, Stanford University, Aug. 1992.

- M. E. Wolf and M. S. Lam. A data locality optimizing algorithm. SIGPLAN Notices, 26(6):30–44, June 1991. Proceedings of the ACM SIGPLAN '91 Conference on Programming Language Design and Implementation.

# Inter-program Compilation for Disk Energy Reduction\*

Jerry Hom and Ulrich Kremer

Rutgers University, Department of Computer Science, Piscataway, NJ 08854, USA {jhom, uli}@cs.rutgers.edu

Abstract. Compiler support for power and energy management has been shown to be effective in reducing overall power dissipation and energy consumption of individual programs, for instance through compilerdirected resource hibernation and dynamic frequency and voltage scaling (DVS). Typically, optimizing compilers perform intra-program analyses and optimizations, i.e., optimize the input program without the knowledge of other programs that may be running at the same time on the particular target machine. In this paper, we investigate the opportunities of compiling sets of programs together as a group with the goal of reducing overall disk energy. A preliminary study and simulation results for this inter-program compilation approach shows that significant disk energy can be saved (between 5% and 16%) over the individually, disk energy optimized programs for three benchmark applications.

#### 1 Introduction

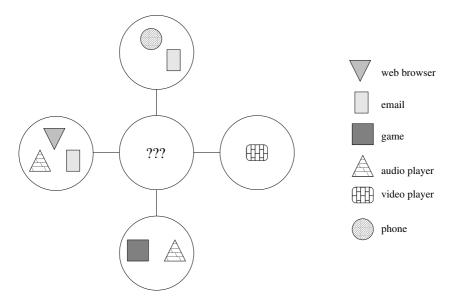

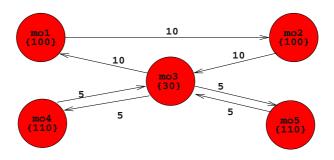

Handheld computers have come a long way from just being a sophisticated address book and calendar tool. Handheld computers or pocket PCs feature rather powerful processors (e.g. 400MHz XScale), 64MB or more of memory, wireless Ethernet connections, and devices such as cameras, speakers, and microphones. They are able to run versions of standard operating systems such as Linux and Windows. However, as compared to their desktop PC counterparts, pocket PCs have significantly less resources, in particular power resources, and less computational capabilities. While pocket PCs will evolve further in terms of their resources and capabilities, they will always be more resource constrained than the comparable desktop PCs, which will evolve as well. As a result, users of pocket PCs have to be more selective in terms of the programs that they wish to store and execute on their handheld computer. Such a program set may include a web browser, an mpeg player, communication software (e.g. ftp), a voice recognition system, a text editor, an email tool, etc. Typically, a user may only run a few of these programs at any given point in time. Figure 1 shows an example of possible subsets of programs executing simultaneously on a handheld PC or

<sup>\*</sup> This work has been partially supported by NSF CAREER award #9985050.

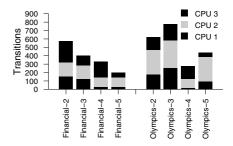

PDA. Only program combinations that occur frequently or are considered important are represented as explicit states. For example, running a web browser, an audio player, and an email program at the same time may occur frequently enough to promise a benefit from inter-program analysis and optimizations. State transitions are triggered by program termination and program activation events. The state marked "???" is a catch-all state that allows internal transitions and represents all combinations of simultaneous program executions that are not considered interesting enough to be analyzed and optimized as a group. The graph shows the underlying assumption of our presented work, namely that a typical usage pattern of a handheld PC or PDA can be characterized by a limited number of program subsets where the programs in a subset are executed together. This makes optimizing particular states or program combinations feasible. The graph can be determined through program traces or other means. Techniques and strategies to determine such a graph are beyond the scope of this paper.

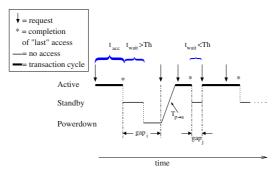

**Fig. 1.** Example finite state machine. Nodes represent subsets of applications executing simultaneously. Transitions are triggered by program activation and termination events. The catch-all state marked "???" allows internal transitions and represents all non-interesting program combinations

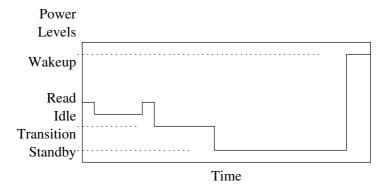

A compiler is able to reshape a program's execution behavior to efficiently utilize the available resources on a target system. Traditionally, efficiency has been measured in terms of performance, but power dissipation and energy consumption have become optimization goals in their own right, possibly trading-off power and energy savings for performance. One effective technique to save power and energy is resource hibernation which exploits the ability of devices to switch between different activity states, ranging from a high activity (active) to a deep sleep state. As a rule of thumb, the lower the activity state, the more power and energy may be saved, but the longer it will take to bring back the device into the fully operational, active state. Each transition between an activity state has a penalty, both in terms of performance and power/energy.

An energy-aware compiler optimization can reshape a program such that the idle times between successive resource accesses are maximized, giving opportunities to hibernate a device more often, and/or in deeper hibernation states. This compilation strategy has been shown to work well in a single process environment[1,2], but may lead to poor overall results in a multiprogramming environment. In a multiprogramming setting, one program may finish accessing a resource and direct the resource to hibernate during some time of idleness. During this time, a second program needs to access the resource. In the worst case, each program alternately accesses a resource such that the resource never experiences significant amounts of idleness. In effect, one program's activity pattern interferes with another program's idle periods and vice versa. To alleviate this problem, some inter-program or inter-process coordination is necessary.

Operating systems techniques such as batch scheduling coordinate accesses to resources across active processes. Requests for a resource are grouped and served together instead of individually, potentially delaying individual requests for the sake of improved overall resource usage. In contrast to operating systems, compilers have often the advantage of knowing about future program behavior and resource requirements. Instead of reacting to resource requests at runtime, a compiler can insert code into a set of programs that will proactively initiate resource usage across the program set at execution time. This is typically beyond the ability of an operating system since it requires program modifications and knowledge about future resource usage.

In this paper, we investigate the potential benefits of an inter-program optimization strategy for disk power and energy management. This paper focuses on a compiler/runtime library based approach, although an OS only, or a combined OS and compiler approach is also possible. An initial study of a compiler only vs. OS only strategy for inter-program optimizations is currently underway.

By considering multiple programs, the compiler applies a synchronization optimization which we call *inverse-barrier*. Previous work has shown that applications which read data from disk in a streamed fashion (i.e., periodic access) can utilize large disk buffers to save energy[1]. These disk buffers are local to each application and serve to increase the idle period between disk accesses. Hence each application has a unique disk access interval associated with the size of its buffer. Having longer intervals between disk accesses creates opportunities to hibernate the disk. This intra-program optimization works well for applications running in isolation, but when multiple such applications execute simultaneously, some of the intra-program optimization's effects are negated. That is, the disk idle period of one application is interrupted by a disk accesses from another application. This will occur whenever the intervals between accesses by multiple applications are different. Simulation experiments using physical traces of three intra-program optimized applications show significant energy savings when applying the inversebarrier optimization. The inverse-barrier also proves more effective at saving energy and maintaining performance than using barrier synchronization.

#### 2 Related Work

This research is related to a few OS level techniques. In order for inter-program compilation to be useful, it should apply optimizations which span across applications. The initial idea began from the notion of a programming mechanism called a barrier to delay disk accesses in order to cluster them as well as increase the idle time between accesses. To be useful, the OS must support such a programming paradigm with a scheduling policy. Indeed, co-scheduling is one example and a well-known technique for scheduling processes in a distributed group at the same time[3]. One aspect is to schedule associated processes at the same time thereby letting processes make progress within their scheduled timeslot. Since our work relies on idleness to save energy, we desire processes to synchronize by scheduling their resource accesses together and maximizing idleness.

Our mechanism for synchronizing accesses, inverse-barrier, is similar to implicit coscheduling for distributed systems[4]. Dusseau et al. introduce a method for coordinating process scheduling by deducing the state of remote processes via normal inter-process communication. The state of a remote process helps the local node determine which process to schedule next. Inverse-barrier applies this idea to coordinate resource accesses by multiple processes on a single system.

More recently, Weissel et al. developed Coop-I/O to address energy reduction by the disk[5]. Coop-I/O enables disk operations to be deferrable and abortable. By deferring operations, the OS may batch schedule them at a later time until necessary. The research also shows some operations may be unnecessary and hence the abortable designation. However, the proposed operations require applications to be updated by using the new I/O function calls. In contrast, our technique utilizes compiler analysis to determine which operations should be replaced. The modification cost is consolidated to the compiler optimization and a recompile of the application.

In terms of scheduling paradigms, this work resembles basic ideas from the slotted ALOHA system[6,7]. The essential idea is to schedule access between multiple users to a common resource (e.g. radio frequency band) while eliminating collisions or when multiple host transmit on the same frequency at the same time. For our purposes, a collision takes on almost the opposite notion of a disk request without any other requests close in time. Rather than scheduling for average utilization of the disk, optimizing for energy means scheduling for bursts of activity followed by long periods of idleness.

A form of inter-program compilation has been applied to a specific problem of enhancing I/O-intensive workloads[8]. Kadayif et al. use program analysis to determine access patterns across applications. Knowledge of access patterns allows the compiler to optimize the codes by transforming naive disk I/O into collective or parallel I/O as appropriate. The benefit manifests as enhanced I/O performance for large, parallel applications. We aim to construct a general framework suitable for developing resource optimizations across applications to reduce energy and power consumption.

#### 3 Intra- Versus Inter-program Optimizations

Handheld computing devices may be designed as general purpose, yet each user may desire to run only a certain mix of applications. If this unique set of applications remains generally unchanging, compiling the set of applications together with inter-program scheduling can enhance performance and cooperation by synchronizing resource usage. A further goal is to show how new energy optimizations may be applied for resource management.

Consider a scheduling paradigm across programs on a single processor. The proposed optimizations augment the paradigm with user-transparent barrier and *inverse*-barrier mechanisms to resemble thread scheduling. Barrier semantics enforce the notion that processes or threads (within a defined group) must pause execution at a defined barrier point until all members of the group have reached the barrier. The notion of an inverse-barrier applies specifically to resources. That is, when a process or thread reaches an inverse-barrier (e.g. by accessing a resource), all members of the group are notified to also access the resource. Synchronizing resource accesses eliminates any pattern of random access and allows longer idle periods where the resource may be placed in a low power hibernation mode.

An example of an intra-program optimization is a transformation to create large disk buffers in memory thereby increasing the disk's idle time for hibernation. While application transformations have been shown to benefit applications executed in isolation[1], running such locally optimized programs concurrently squander many of the benefits because the access pattern from each process disrupts the idle time of the resource. This intra-program optimization considers each program by itself while an inter-program optimization now considers all programs in a group and augments them to cooperate in synchronizing accesses to a resource.

Program cooperation can be accomplished in at least two ways: (1) delay resource access until all group members wish to use it or (2) inform all group members to use the resource immediately. The first method is similar to a barrier mechanism in parallel programming and can be used by programs which lack deadlines. The second method has the notion of an inverse-barrier and can be used by programs with deadline constraints such as real-time software.

Programs using a barrier cooperate in a passive fashion. When a program wants to access a resource, it will pause and wait until all members in its group also wish to access the resource. When all members reach the barrier, then they all may access the resource consecutively. To avoid starvation, each waiting process has a timer. If the timer expires, the process will proceed to access the resource.

Programs using an inverse-barrier cooperate actively to synchronize resource accesses. When a program needs to access a resource, it will notify all members in its group to also access the resource immediately. This has the effect of refilling a program's disk buffer earlier than necessary which ensures that deadlines are satisfied. This synchronization mechanism can be communicated via signals among all processes. Only those processes with an appropriately included signal handler will follow suit in accessing the resource. Uninterested processes may simply ignore the signal.

The signal mechanism is also used in our current compilation framework to inform active programs about other active, simultaneously executing programs. The compiler generates signal handling code within each program that implements state transitions between interesting groups of applications. Each time a program is about to terminate, it sends a signal to inform other active processes about its termination event. The appropriate signal handlers in the remaining active programs will then make the corresponding state transition. Each time a program begins execution, it sends a signal to inform other active programs about its presence. In return, active programs will send a signal informing the "new" process about the state that they are in, i.e., inform the program about its current execution group. This way, a program is aware of its group execution context, and can perform appropriate optimizations in response to inverse-barrier signals.

#### 4 Experiments and Results

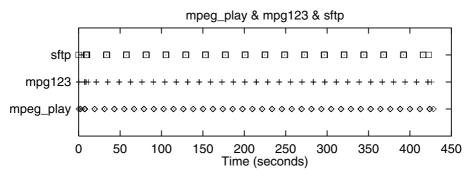

This benefit analysis builds upon previous work and examines three streaming applications *mpeg\_play*, *mpg123*, and *sftp*. The MPEG video and audio decoders are examples of real-time applications where they must have low latency access to the disk. They cannot afford to wait for other applications before accessing the disk. On the other hand, ftp is a silent process, mostly invisible to the user, and can tolerate pauses with the understanding that throughput performance is traded off with energy savings.

From these three applications, there are three experiments with interesting results: 1) all three applications, 2) video with audio, 3) audio with ftp. Combining video with ftp is expected to produce similar results as (3). Although the original experiments operated on the same file, each run produced slightly different traces because of the dynamic nature of the disk profiling at program startup. However, the variance from each set of runs was minor and demonstrates the stability of the profiling strategy. All experiments used disk traces from Heath et al.[1] for hand simulating the behavior of these programs executing at the same time with and without inter-program optimizations applied.

The disk traces were modified to better simulate the more interesting, steady state conditions while the applications are running simultaneously. The duration of the traces from the three programs vary considerably. For example, the trace for mpg123 lasted 425 seconds while  $mpeg_play$  and sftp were 106 and 232 seconds, respectively. The shorter traces were extended to be roughly time equivalent to mpg123. Since each program was optimized to produce periodic disk accesses, extending the execution time is merely a matter of using larger data files. Hence, the traces were extended by "copying and pasting" multiples of disk access periods.

A second modification deals with the buffer sizes. The buffer size is calculated at runtime after some profiling steps. A prudent calculation would divide the buffer size by n where n is the number of applications compiled with this disk buffer optimization. Otherwise, if all applications used its maximums buffer size, thrashing may occur when such applications are actually executed together. Thus, the disk access intervals for each application was divided by either 2 or 3 for the experiments.

These particular applications lightly stress the CPU, and the experiments assume that the CPU meets all deadlines (e.g. decoding frames) for all applications running simultaneously. The CPU can decode all frames of video and audio while copying blocks of data for file transfer without degrading performance. Degraded performance might result in dropped frames. However, the physical disk is constrained to serving one process at a time. Thus, if more than one process issues a disk request at the same time, they will be queued and interleaved. In effect, disk access time by processes cannot be overlapped and hidden.

The results of these experiments are closely tied to system parameters. A different disk will change the mix of thresholds in determining when to switch power states, but the essential premise is the potential to save energy by utilizing low power states. Table 1 summarizes the parameters measured on a real disk[1]. When transitioning from *idle* to *standby*, the disk spends 5.0 seconds in the *transition* state. When waking up from *standby* to *idle* or *read*, the disk takes 1.6 seconds. The idleness threshold at which transitioning to *standby* becomes profitable is 10.0 seconds. That is, when the system knows the next disk access is greater than 10.0 seconds, the system should tell the disk to transition to *standby*.

Table 1. Disk states and power levels

| Disk States | Power (W) |

|-------------|-----------|

| wakeup      | 3.0       |

| read        | 1.8       |

| idle        | 0.9       |

| transition  | 0.7       |

| standby     | 0.2       |

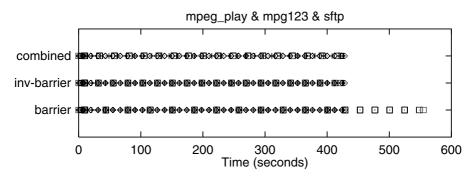

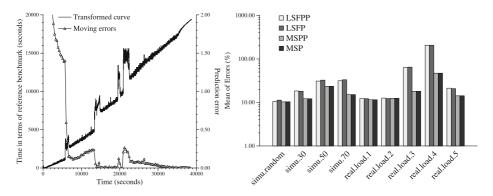

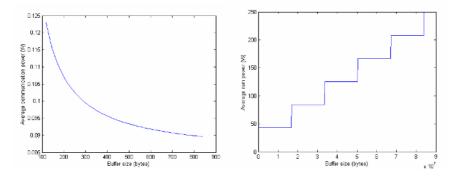

The first experiment combines all three applications. The respective disk access periods are  $P_{mpeg\_play} = 11.7$ ,  $P_{mpg123} = 13.7$ , and  $P_{sftp} = 23.5$ ; all times in seconds. Figure 2 shows the disk access traces of each application. The top

Fig. 2. Disk access traces for mpeg\_play, mpg123, and sftp

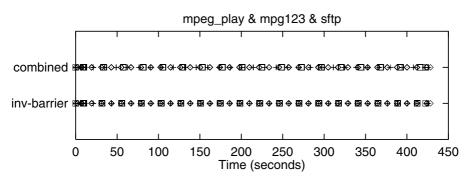

Fig. 3. Running all three applications simultaneously. Comparison of disk access patterns with inverse-barrier optimization for synchronization. Inverse-barrier scheduling saves 5.4% energy

row of Figure 3 shows an overlay of all disk accesses. The bottom row shows the synchronization when using inverse-barrier scheduling. Net energy savings is 5.4%.

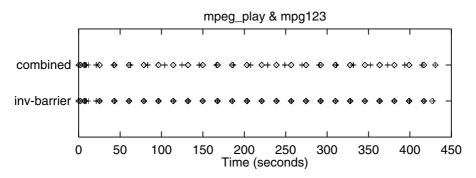

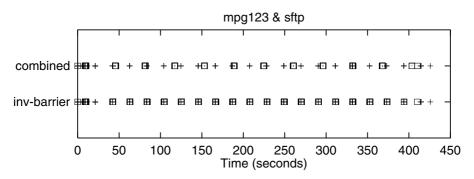

The second experiment combines  $mpeg_play$  with mpg123. The disk access periods are  $P_{mpeg_play} = 17.6$  and  $P_{mpg123} = 20.6$ . Figure 4 illustrates the idleness interference patterns of just two applications vs. inverse-barrier synchronization. A similar pattern can be seen with the third experiment in Figure 5. Here, the disk access periods are  $P_{mpg123} = 20.6$  and  $P_{sftp} = 35.2$ . The energy saved in these two experiments are 15.9% and 9.8%, respectively.

There is a key difference between the inverse-barrier and barrier mechanisms. An OS may employ a barrier mechanism to delay resource accesses for applications which can tolerate such latencies. For example, *sftp* has few constraints about deadlines since it operates by best effort semantics over an unreliable network. If an OS uses this assumption to schedule *sftp* with barriers at disk accesses (i.e., delaying until next access by another application), there will certainly be a performance delay. This mode of operation can still save energy by batching the disk access but also depending on how much delay is involved. The difference with inverse-barrier is the pre-emptive action to ensure that buffers are always

Fig. 4. Comparison of two applications' (*mpeg\_play*, *mpg123*) disk access patterns. Inverse-barrier scheduling saves 15.9% energy

Fig. 5. Comparison of two applications' (*mpg123*, *sftp*) disk access patterns. Inversebarrier scheduling saves 9.8% energy

sufficiently full. At every synchronized disk access, each process can check the data capacity of its buffer and decide whether to read more data. Another optimization during the buffer check might compute the differential between resource access periods. For instance, if a process has a resource access period more than twice as long as the current period, it can afford to skip every other resource access and maintain a non-empty buffer.

The last experiment explores the behaviors of barrier scheduling; Figure 6 illustrates the difference. In terms of execution time, sftp finishes over two minutes later using the barrier vs. the inverse-barrier. Compared to the baseline of running all applications together under normal scheduling, the barrier method expends 2.4% more energy. Barrier scheduling is only slightly more expensive in energy yet can impact performance. In this case, sftp's performance is delayed by 31.4%. Under inverse-barrier scheduling, there is no performance loss while showing modest energy savings.

Fig. 6. Comparison of intra-program buffered I/O optimizations, with inter-program inverse-barrier scheduling, and with barrier scheduling on *sftp*. Barrier scheduling causes *sftp* to finish 132 seconds later, a 31.4% performance delay, while using 2.4% more disk energy overall

#### 5 Analysis of Potential Energy Savings

Investigating the upper bounds on energy savings gives an indication whether this avenue of research is worthwhile. Exploring the involved parameters can provide insights into how this technique is beneficial. Towards that end, consider a situation of two programs, A and B, optimized to exhibit periodic resource access behavior. Inter-program compilation with inverse-barrier scheduling results in our optimized execution, but how much can it possibly save over the previous intra-program optimization, which has already shown large disk energy savings? We can approximate this with an analytical examination of the cases where the intra-program execution deviates from the optimal case where all programs access a resource at the same time (i.e., in batch mode). Our inter-program optimization results in such an optimal case. Thus, the difference represents the potential energy savings.

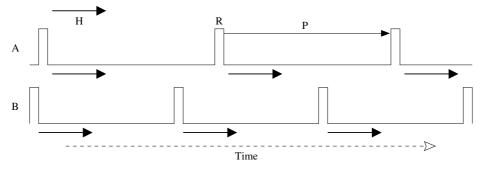

Refer to Table 2 for a list of involved parameters. The following description of these parameters are illustrated in Figure 7. Hence,  $P_A$  and  $P_B$  represent the period between resource accesses by programs A and B; assume  $\frac{P_A}{2} < P_B < P_A$ and let  $\Delta P = P_A - P_B$ . Each program accesses the resource for an amount of time,  $R_A$  and  $R_B$ . The rise and fall in the graphs of programs A and B merely indicate a resource access. Only one resource is considered, so its corresponding hibernation threshold time will be designated simply H. If a resource will be idle for at least H, then hibernation will be beneficial and assumed to be initiated. Consequently, we assume  $min(P_i) > H$ ; otherwise any chance for hibernation is gone.

There are three ways to categorize the resource access patterns, demonstrated by the three accesses of A ( $A^1$ ,  $A^2$ ,  $A^3$ ) along with the four accesses of B ( $B^1$ ,  $B^2$ ,  $B^3$ ,  $B^4$ ).  $A^1$  is optimal because it is clustered with  $B^1$ . Since the resource will not be used again within H of  $A^1$ , hibernation may be initiated immediately.  $A^2$  is sub-optimal because it occurs within H of  $B^2$ . The accesses are mildly offset, and the resource consumes extra energy by remaining in the idle power

Table 2. Analytical parameters

| Variable | Description                                 |

|----------|---------------------------------------------|

| $P_i$    | resource access Period of program $i$       |

| $R_i$    | length of access (Read) time by program $i$ |

| $H_i$    | Hibernation threshold of resource $i$       |

| $E_i$    | average Energy use in case $i$              |

Fig. 7. Resource access patterns of programs A and B

state.  $A^3$  is *out-of-phase* because it occurs after H of  $B^3$ , and  $B^4$  occurs after H of  $A^3$ . The effect is that  $B^3$ 's and  $A^3$ 's hibernation periods are immediately interrupted. There is little opportunity to save energy during the respective hibernation periods. The next question is, what percentage of time do each of the three cases occur?

The optimal case, *opt*, can be expected to occur  $\frac{\Delta P}{P_B}\%$  of the time. If A and B have a synchronized access, then each respective access afterward will be offset by  $\Delta P$ . They will coincide again after  $\frac{P_B}{\Delta P}$  accesses. The sub-optimal case is expected to occur  $sub-opt = (max(\frac{2H}{P_B}, 1) - opt)\%$  of the time. The first term refers to all accesses within H of an access, including the optimal case. Subtracting the optimal case gives just the sub-optimal case. Lastly, the out-of-phase case occurs out = (1 - (opt + sub-opt))% of the time, or simply the remaining percentage of time after subtracting the optimal and sub-optimal cases.

The next step toward estimating potential energy savings is calculating the average energy consumed during the three cases and computing the differences. The energy usage for each case can be obtained from a power consumption profile which is a simple graph showing the amount of time spent in the various power states. In the non-optimal cases, there may be many instances of the graphs corresponding to different timing offsets between accesses. These are averaged to produce one profile graph for each of the sub-optimal and out-of-phase cases. Figure 8 shows what a sample power profile may look like. The average energy usage of each case,  $E_i$ , is now a matter of summing the power levels over time.

Finally, with the average energy use of all three cases  $(E_{opt}, E_{sub-opt}, E_{out})$ , an upper bound on potential energy savings can be computed. Energy savings

Fig. 8. Sample power profile graph

over the sub-optimal case is  $\Delta E_{sub-opt} = E_{sub-opt} - E_{opt}$ , and the out-of-phase case is  $\Delta E_{out} = E_{out} - E_{opt}$ . These cases occur *sub-opt* and *out* percent of the time. Thus, the upper bound is  $(sub-opt * \frac{\Delta E_{sub-opt}}{E_{opt}}) + (out * \frac{\Delta E_{out}}{E_{opt}})$ . Applying this analysis to the experiment of running *mpeg\_play* and *mpg123* together under inter-program optimization, the upper bound is estimated at 26.2% while actual savings is 15.9%. The upper bound can never be reached because of the small overhead involved during program startup for profiling to initialize the disk buffers. For this experiment, the startup overhead accounted for 5.8% of the total execution time.

#### 6 Summary and Future Work

Inter-program optimization is a promising new compilation strategy for sets of programs that are expected to be executed together. Such sets occur, for instance, in resource restricted environments such as handheld, mobile computers. Resource usage can be coordinated across all programs in the set, allowing additional opportunities for resource hibernation over single program, i.e., intra-program, optimizations alone. This paper discussed the potential benefits of inter-program analysis using the disk as the resource. An analysis of energy savings and simulation results for a set of three benchmark programs show that further significant energy savings over intra-program optimizations (between 5% and 16% for the simulations) can be achieved.

The compiler and OS have unique perspectives on key parts of the entire resource management scheme. We hope to experimentally explore and discover the strengths from each, then apply them in developing a resource-aware compiler and OS system. A current study is trying to assess the advantages and disadvantages of a compiler-only; compiler and runtime system; OS-only; and compiler, runtime system and OS approach to inter-program resource management. We will also be using physical measurements to guide and validate our development efforts.

25

#### References

- Heath, T., Pinheiro, E., Hom, J., Kremer, U., Bianchini, R.: Application transformations for energy and performance-aware device management. In: Proceedings of the Conference on Parallel Architectures and Compilation Techniques. (2002) Best Student Paper Award.

- Delaluz, V., Kandemir, M., Vijaykrishnan, N., Irwin, M., Sivasubramaniam, A., Kolcu, I.: Compiler-directed array interleaving for reducing energy in multi-bank memories. In: Proceedings of the Conference on VLSI Design. (2002) 288–293

- 3. Ousterhout, J.: Scheduling techniques for concurrent systems. In: Proceedings of the Conference on Distributed Computing Systems. (1982)

- Arpaci-Dusseau, A., Culler, D., Mainwaring, A.: Scheduling with implicit information in distributed systems. In: Proceedings of the Conference on Measurement and Modeling of Computer Systems. (1998) 233–243

- Weissel, A., Beutel, B., Bellosa, F.: Cooperative I/O a novel I/O semantics for energy-aware applications. In: Proceedings of the Conference on Operating Systems Design and Implementation. (2002)

- Abramson, N.: The ALOHA system another alternative for computer communications. In: Proceedings of the Fall Joint Computer Conference. (1970) 281–285

- 7. Roberts, L.: ALOHA packet system with and without slots and capture. Computer Communications Review 5 (1975) 28–42

- 8. Kadayif, I., Kandemir, M., Sezer, U.: Collective compilation for I/O-intensive programs. In: Proceedings of the IASTED Conference on Parallel and Distributed Computing and Systems. (2001)

# Energy Consumption in Mobile Devices: Why Future Systems Need Requirements–Aware Energy Scale-Down

Robert N. Mayo and Parthasarathy Ranganathan

Hewlett Packard Labs, 1501 Page Mill road MS 1177, Palo Alto California 94304 {Bob.Mayo, Partha.Ranganathan}@hp.com

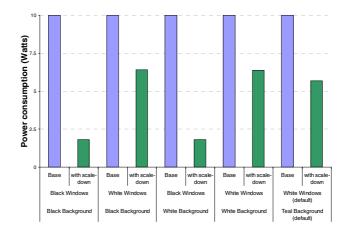

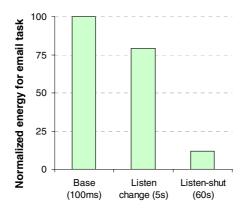

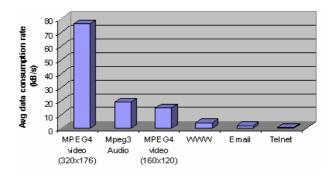

Abstract. The current proliferation of mobile devices has resulted in a large diversity of designs, each optimized for a specific application, form-factor, battery life, and functionality (e.g., cell phone, pager, MP3 player, PDA, laptop). Recent trends, motivated by user preferences towards carrying less, have focused on integrating these different applications in a single general-purpose device, often resulting in much higher energy consumption and consequently much reduced battery life. This paper argues that in order to achieve longer battery life, such systems should be designed to include requirements-aware energy scale-down techniques. Such techniques would allow a general-purpose device to use hardware mechanisms and software policies to adapt energy use to the user's requirements for the task at hand, potentially approaching the low energy use of a special-purpose device. We make two main contributions. We first provide a model for energy scale-down. We argue that one approach to design scale-down is to use special-purpose devices as examples of powerefficient design points, and structure adaptivity using insights from these design points. To understand the magnitude of the potential benefits, we present an energy comparison of a wide spectrum of mobile devices (to the best of our knowledge, the first study to do so). A comparison of these devices with general-purpose systems helps us identify scale-down opportunities. Based on these insights, we propose and evaluate three specific requirements-aware energy scale-down optimizations, in the context of the display, wireless, and CPU components of the system. Our optimizations reduce the energy consumption of their targeted subsystems by factors of 2 to 10 demonstrating the importance of energy scale-down in future designs.

#### **1** Introduction

Recent advances in computing and communication have led to increased use of a large number of mobile computing devices. These devices have many purposes and form-factors including both general-purpose devices like laptops, pocket PCs, and palm computers as well as specialized devices like portable MP3 players and e-mail pagers. Both form factor and energy are critical resources for all these devices, forcing users to trade away functionality to gain smaller form factors and longer battery

© Springer-Verlag Berlin Heidelberg 2004

lifetimes. A variety of such tradeoffs exist for many specific tasks. For instance, the email task can be accomplished with a feature-rich and high-energy application like Microsoft Outlook running on a laptop, or a reduced-feature low-energy application like a Blackberry email pager<sup>1</sup>.

The drive for small form factors is strong, resulting in users demanding the most value from a given form factor. The popularity of camera/cell phone combinations are examples of multiple applications in a single device, with a consequent reduction in overall form factor when compared to the sum of two separate devices. Most successfully-converged products combine applications with similar hardware and software requirements. In our example, both cameras and cell phones can share a processor with limited computational power, a common display, and a small set of input buttons. But different applications inherently have some mismatch. Higher-resolution color displays are needed on camera/phone combinations compared to stand-alone mobile phones, leading to increased energy use even when only using the phone portion of the device.

Perhaps the best examples of this mismatch are in general-purpose devices like PDAs. These devices can run a wide range of software and accept a wide range of hardware cards. Thus, they would appear to be the ultimate device for handheld convergence. But this generality currently comes at the cost of high energy use, making the devices much less attractive. The main reason for this is the lack of adaptability in the hardware and software energy use.

Consider a comparison of two email applications: feature-rich email software running on a high-end handheld computer versus an email pager. Both handle the email task well, but with different tradeoffs between functionality and battery life. In the case of the pager, users want long battery life, notification of incoming email, and an acceptable screen for text. Much less important is the ability to view color photographs or read attached files. If the user of a handheld computer desires the reduced features and longer battery life, it is largely unobtainable. It simply is not possible to run a pager-like application on a high end handheld computer and get pager-like battery life.

Application-specific devices like cell phones, email pagers, and MP3 players are examples of highly successful tradeoffs of functionality, form-factor, and battery life. Their success proves them to be excellent points in the design space, in that users find high value in them. As such, they can serve as benchmarks against which we can compare general-purpose devices. A truly general-purpose device should strive to emulate these design points, including not only the specific functionality but also the battery life.

While there are many technical challenges, *requirements-aware energy scale-down* is an approach that can yield improvements. The idea is to have both hardware and software that can scale their features and energy use to meet a variety of design points. For high functionality, hardware and software would present a rich set of features to

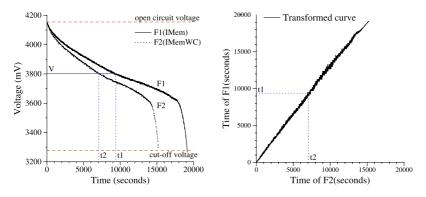

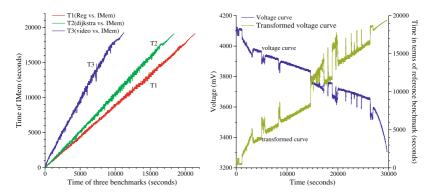

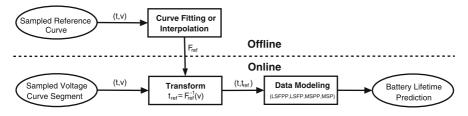

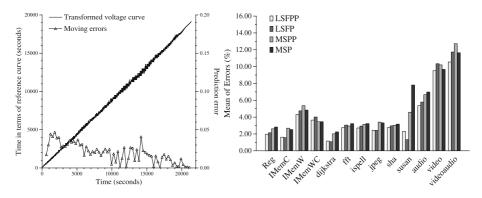

<sup>&</sup>lt;sup>1</sup> In this paper, we use the terminology *task* to mean a broad category, such a music listening task or an email task. A specific set of hardware and software to accomplish this task is called an *application*, and involves various tradeoffs of functionality, battery life, and form factor. For instance, the music listening task could be accomplished using either a PDA or a tiny MP3 player.